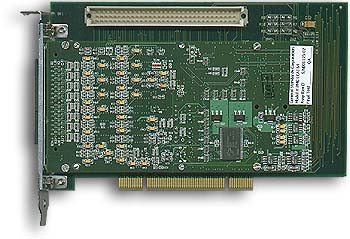

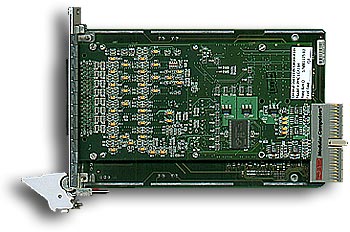

The PC104P66-18AI32SSC1M analog input board samples and digitizes up to 32 input channels simultaneously at rates up to 1,000,000 samples per second for each channel. Native conversion resolution is available as either 18 bits or 16 bits. Data on native 18-Bit boards can be configured as either 16 or 18 bits. Each input channel contains a dedicated successive-approximation (SAR) ADC, the sampled data from which is error-corrected and routed to the PC104+ bus through a 1-MByte FIFO buffer. The 32-Bit local data path supports full D32 local-bus data packing for 16-Bit data. Throughput performance is further enhanced with 66MHz PC104+ support. All operational parameters are software configurable.

Inputs can be sampled in groups of 2, 4, 8, 16, or 32 channels, or any contiguous channel group can be designated for acquisition. The sample clock can be generated from an internal rate generator, or by software or external hardware. Input ranges are software-selectable as ±10V or ±5V, or optionally as ±2.5V or ±1.25V. Continuous background calibration can be invoked at lower sample rates.

An on-demand autocalibration feature determines offset and gain correction values for each input channel, and applies the corrections subsequently during acquisition. For low sample rates, below 750SPS, continuous autocalibration can be invoked to minimize both short-term and long-term drift errors. A selftest switching network routes calibration reference signals to each channel through internal selftest switches, and permits board integrity to be verified by the host.