The DAC_3113 is the third member of FMC VITA 57.1 data acquisition product line integrated by the ADC_3110 (16-bit 250Msps ADC with AC coupling), and the ADC_3111 (16-bit 250Msps ADC with DC coupling).

The dual 16-bit 250Msps ADC channels are implemented with a DC coupled front-end preamplifier, through four (4) SSMC connectors. The analog ADC inputs can be configured to operate in single-ended or differential mode.

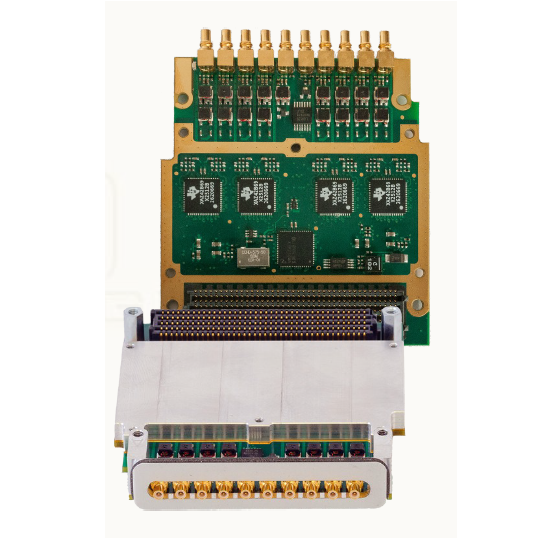

The dual 16-bit 250/500Msps DAC channels are implemented in differential mode with outputs routed to a eSATA II differential connector. The DAC AD9783 output stage is powered with ultra low-noise power supplies built with a 2 level cascaded LDO.

A 6th order Bessel passive filter is implemented in both DAC output paths.

The on-board clock tree is implemented with a high-precision low-jitter low-phase noise clock fully programmable controller LMK04906. Input clock reference can be selected either from the on-board XCO or from the front panel SSMC CLKREF

.